### **General Description**

The MAX14500–MAX14503 USB-to-SD™ card readers provide a means for portable devices that support fullspeed USB communication (12Mbps) with one or two SD card slots, upgrading the USB SD card reader function to USB Hi-Speed (480Mbps) operation. The MAX14500-MAX14503 have two modes of operation: Pass Thru and Card Reader. In pass thru, the SD and USB signals pass through the MAX14500-MAX14503 without modification, appearing like the device is not present. The host microprocessor firmware does not need modification, as there is no change from the host microprocessor's perspective. In Card Reader mode, the MAX14500-MAX14503 implement a Hi-Speed USB card reader that operates independently of the host microprocessor. All the capabilities of the full-speed USB port and SD card slot are preserved with the additional feature that allows a faster way for a PC to read or write to the SD card. The MAX14500-MAX14503 support SD high capacity SDHC cards. The 40-pin TQFN version supports one SD card, while the 56-bump WLP version supports two SD cards.

The MAX14500–MAX14503 feature advanced powersaving modes to reduce power consumption in portable applications. The low-power Sleep modes allow the ability to disable internal circuit blocks, providing power-saving operating modes. The default clock input for each part number is specified in the ordering information. The MAX14500–MAX14503 feature the option to change the default values using the I<sup>2</sup>C interface.

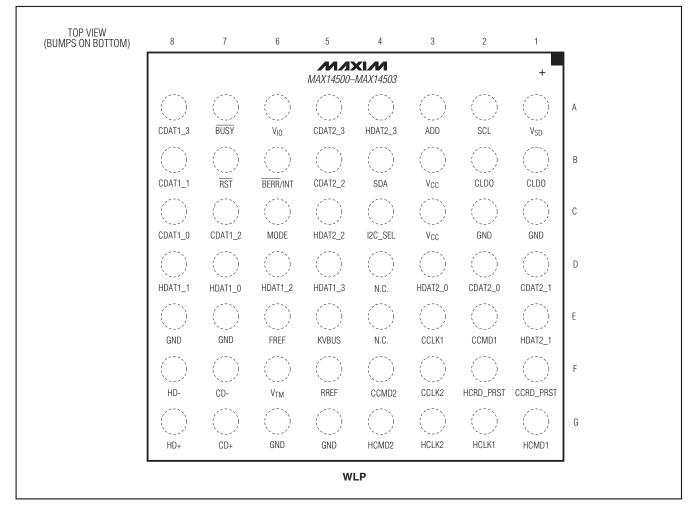

The MAX14500–MAX14503 are available in 5mm x 5mm, 40-pin TQFN, and 3.23mm x 3.5mm, 56-bump WLP packages. These devices operate over a wide supply voltage range and are specified over the -40°C to +85°C extended temperature range.

### **Applications**

Cell Phones PDAs MP3 Players Digital Still Cameras GPS

### **Features**

- USB 2.0 Hi-Speed and Full-Speed Compliant

- SDHC Card Support

- Internal Hi-Speed USB SD Card Reader Eases Host µP Overhead

- On-Chip Termination and Pullup Resistors

- Internal SD Switches Allow For Multiplexing Two SD Cards on a Single-Microprocessor SD Port

- Accommodates Clock Input Frequencies 26MHz, 19.2MHz, 13MHz, and 12MHz

- Internal Clock Squarer for Low-Amplitude TCXO Signals

- No Power-Supply Sequencing Required

- Compatible with +1.8V to +3.3V I/O Host Microprocessor

- Simple Control Mode Requires Only a Single GPIO

- I<sup>2</sup>C Control Provides Multiple Configuration Options

- ♦ I<sup>2</sup>C Control Required for Two SD Cards

- ♦ On-Chip Power-On Reset/Brown-Out Reset

### Ordering Information/ \_\_\_\_\_Selector Guide

| PART           | INPUT<br>FREQUENCY<br>(MHz) | SD<br>CARDS | PIN-<br>PACKAGE |

|----------------|-----------------------------|-------------|-----------------|

| MAX14500ETL+*  | 12                          | 1           | 40 TQFN-EP**    |

| MAX14500AEWN+* | 12                          | 2           | 56 WLP          |

| MAX14501ETL+*  | 13                          | 1           | 40 TQFN-EP**    |

| MAX14501AEWN+* | 13                          | 2           | 56 WLP          |

| MAX14502AETL+  | 19.2                        | 1           | 40 TQFN-EP**    |

| MAX14502AEWN+* | 19.2                        | 2           | 56 WLP          |

| MAX14503ETL+*  | 26                          | 1           | 40 TQFN-EP**    |

| MAX14503AEWN+* | 26                          | 2           | 56 WLP          |

**Note:** All devices are specified over the -40°C to +85°C operating temperature range.

+Denotes a lead(Pb)-free/RoHS-compliant package.

\*Future product—contact factory for availability.

\*\*EP = Exposed pad.

SD is a trademark of the SD Card Association.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

(All voltages referenced to GND.)

| (All vollages relefenced to GIVL | /.)                                  | СО+, СО-, ПО+, П   |

|----------------------------------|--------------------------------------|--------------------|

| V <sub>CC</sub>                  | -0.3V to +4V                         | Continuous Power   |

| V <sub>SD</sub>                  | 0.3V to +4V                          | 40-Pin TQFN (de    |

| V <sub>IO</sub>                  | 0.3V to +4V                          | Junction-to-Case T |

| V <sub>TM</sub>                  | 0.3V to +4V                          | 40-Pin TQFN        |

| KVBUS                            | 0.3V to +4V                          | Junction-to-Ambier |

|                                  | 0.3V to +2V                          | 40-Pin TQFN        |

| CDAT1_[3:0], HDAT1_[3:0], CC     | MD1, HCMD1, CCLK1, HCLK1,            | Operating Temper   |

|                                  | CDAT2_[3:0], HDAT2_[3:0],            | Junction Temperat  |

| CCMD2, HCMD2, CCLK2, HC          | CLK20.3V to (V <sub>SD</sub> + 0.3V) | Storage Temperati  |

| BUSY, BERR/INT, MODE, SCL,       | SDA, I2C_SEL,                        | Lead Temperature   |

| ADD, <u>RST</u>                  | 0.3V to (V <sub>IO</sub> + 0.3V)     |                    |

|                                  |                                      |                    |

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a fourlayer board. For detailed information on package thermal considerations, refer to <u>www.maxim-ic.com/thermal-tutorial</u>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.4V \text{ to } +3.6V, V_{SD} = +2.4V \text{ to } +3.6V, V_{IO} = +1.5V \text{ to } +3.6V, V_{TM} = +2.91V \text{ to } +3.4V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.} Typical values are at V_{CC} = +3.3V, V_{IO} = +2.5V, V_{SD} = +2.5V, V_{TM} = +3.3V, T_A = +25^{\circ}\text{C}.) (Note 2)$

| PARAMETER                                    | SYMBOL            | CONDITIONS                                      | MIN  | ТҮР | MAX | UNITS |  |

|----------------------------------------------|-------------------|-------------------------------------------------|------|-----|-----|-------|--|

| DC CHARACTERISTICS                           |                   | ·                                               |      |     |     | •     |  |

|                                              |                   | Pass thru                                       | 2.1  |     | 3.6 | V     |  |

| V <sub>CC</sub> Supply Voltage               | V <sub>CC</sub>   | Card reader active, f <sub>CCLK</sub> _ ≤ 26MHz | 2.1  |     | 3.6 |       |  |

|                                              |                   | Card reader active, f <sub>CCLK</sub> > 26MHz   | 2.4  |     | 3.6 |       |  |

|                                              |                   | Pass thru                                       | 2.0  |     | 3.6 |       |  |

| V <sub>SD</sub> Supply Voltage               | V <sub>SD</sub>   | Card reader active, f <sub>CCLK</sub> ≤ 26MHz   | 2.0  |     | 3.6 | V     |  |

|                                              |                   | Card reader active, f <sub>CCLK</sub> > 26MHz   | 2.4  |     | 3.6 |       |  |

| Logic Interface Supply Voltage               | VIO               |                                                 | 1.5  |     | 3.6 | V     |  |

| USB Supply Voltage                           | V <sub>TM</sub>   |                                                 | 2.91 |     | 3.4 | V     |  |

| Digital Core LDO Regulator<br>Output Voltage | V <sub>CLDO</sub> | $C_{CLDO} = 1.0 \mu F$                          |      | 1.8 |     | V     |  |

| Maa Curahu Currant                           | ICC               | Pass thru                                       |      | 5   | 15  | μΑ    |  |

| V <sub>CC</sub> Supply Current               |                   | Card reader active                              |      | 35  | 50  | mA    |  |

| Vez Supply Current                           |                   | Pass thru                                       |      | 17  | 40  | μA    |  |

| V <sub>SD</sub> Supply Current               | I <sub>SD</sub>   | Card reader active                              |      | 3   |     | mA    |  |

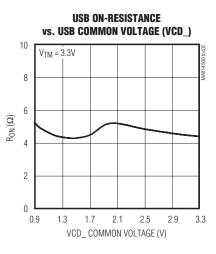

| VIO Supply Current                           | lio               | Pass thru                                       |      | 2   | 10  | μA    |  |

| VIO Supply Current                           | lio               | Card reader active                              |      | 0.2 |     | mA    |  |

| Vta Supply Current                           | l The             | Pass thru                                       |      | 13  | 50  | μA    |  |

| V <sub>TM</sub> Supply Current               | ITM               | Card reader active                              |      | 25  |     | mA    |  |

| V <sub>SD</sub> Comparator Threshold         | VSDCT             |                                                 | 1.0  | 1.5 | 1.9 | V     |  |

| V <sub>TM</sub> Comparator Threshold         | V <sub>TMCT</sub> |                                                 | 2.0  | 2.5 | 2.9 | V     |  |

| MODE, I2C_SEL, ADD, RST<br>Input-Voltage Low | VIL               |                                                 |      |     | 0.4 | V     |  |

///XI//

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.4V \text{ to } +3.6V, V_{SD} = +2.4V \text{ to } +3.6V, V_{IO} = +1.5V \text{ to } +3.6V, V_{TM} = +2.91V \text{ to } +3.4V, T_A = -40^{\circ}C \text{ to } +85^{\circ}C$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$ ,  $V_{IO} = +2.5V$ ,  $V_{SD} = +2.5V$ ,  $V_{TM} = +3.3V$ ,  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                     | SYMBOL              | CONDITIONS                                                                   | MIN                       | ТҮР  | МАХ                        | UNITS |

|-----------------------------------------------|---------------------|------------------------------------------------------------------------------|---------------------------|------|----------------------------|-------|

| MODE, I2C_SEL, ADD, RST<br>Input-Voltage High | VIH                 |                                                                              | 2/3 x<br>V <sub>IO</sub>  |      |                            | V     |

| BUSY, BERR/INT<br>Output-Voltage Low          | Vol                 | I <sub>LOAD</sub> = 1mA                                                      |                           |      | 0.4                        | V     |

| BUSY, BERR/INT<br>Output-Voltage High         | V <sub>OH</sub>     | I <sub>LOAD</sub> = -1mA                                                     | V <sub>IO</sub> -<br>0.4  |      |                            | V     |

| I2C_SEL, ADD, RST Input<br>Leakage Current    | Ι <sub>Ι</sub> Γ    |                                                                              | -1                        |      | +1                         | μA    |

| MODE Input Resistance to GND                  | RMODE               |                                                                              | 150                       | 300  | 500                        | kΩ    |

| FREF Full-Swing Input-Voltage<br>High         | VIH                 |                                                                              | 1.3                       |      |                            | V     |

| FREF Full-Swing Input-Voltage<br>Low          | VIL                 |                                                                              |                           |      | 0.4                        | V     |

| FREF Low-Amplitude Input-<br>Voltage Low      | VIL                 |                                                                              | 200                       |      |                            | mV    |

| FREF Input Leakage Current                    | lilf                | Full-Swing mode                                                              | -10                       |      | +10                        | μA    |

| FREF Input Resistance                         |                     | Low-Amplitude input mode                                                     |                           | 1    |                            | MΩ    |

| KVBUS Comparator Threshold                    | VTH                 |                                                                              | 1.0                       | 1.25 | 1.5                        | V     |

| KVBUS Comparator Hysteresis                   | V <sub>HYS</sub>    |                                                                              |                           | 20   |                            | mV    |

| KVBUS Comparator Input<br>Impedance           | R <sub>IN</sub>     |                                                                              | 10                        |      |                            | MΩ    |

| SDA/SCL Input Low Voltage                     | VIL_I2C             |                                                                              |                           |      | 0.3 x<br>V <sub>IO</sub>   | V     |

| SDA/SCL Input High Voltage                    | VIH_I2C             |                                                                              | 0.7 x<br>V <sub>IO</sub>  |      |                            | V     |

|                                               |                     | V <sub>IO</sub> > +2V, 3mA sink current                                      | 0                         |      | 0.4                        |       |

| SDA Output Logic-Low                          | V <sub>OL_I2C</sub> | $V_{IO} \le +2V$ , 3mA sink current                                          | 0                         |      | 0.2 x<br>V <sub>IO</sub>   | V     |

| SDA/SCL Input Leakage Current                 | IIN_I2C             |                                                                              | -10                       |      | +10                        | μA    |

| SD CARD INTERFACE                             |                     | ·                                                                            |                           |      |                            |       |

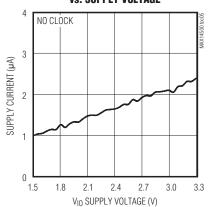

| On-Resistance                                 | Ron                 | V <sub>TEST</sub> = 0 or V <sub>SD</sub> , I <sub>TEST</sub> = 10mA (Note 3) |                           | 10   |                            | Ω     |

| Off-Leakage Current                           | lilsd               | V <sub>TEST</sub> = 0 or V <sub>SD</sub> (Note 3)                            | -1                        |      | +1                         | μA    |

| Off-Capacitance                               | C <sub>SD_OFF</sub> | (Note 4)                                                                     |                           | 5    |                            | pF    |

| On-Capacitance                                | C <sub>SD_ON</sub>  | (Note 5)                                                                     |                           | 10   |                            | pF    |

| Pullup Resistance                             | R <sub>PU</sub>     | CCMD1, CCMD2, CDAT1_[3:0],<br>CDAT2_[3:0]                                    | 50                        | 75   | 100                        | kΩ    |

| Output High Voltage                           | Vон                 | I <sub>OH</sub> = -100μA                                                     | 0.75 x<br>V <sub>SD</sub> |      |                            | V     |

| Output Low Voltage                            | Vol                 | I <sub>OL</sub> = 100μA                                                      |                           |      | 0.125 x<br>V <sub>SD</sub> | V     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.4V \text{ to } +3.6V, V_{SD} = +2.4V \text{ to } +3.6V, V_{IO} = +1.5V \text{ to } +3.6V, V_{TM} = +2.91V \text{ to } +3.4V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$ noted. Typical values are at V<sub>CC</sub> = +3.3V, V<sub>IO</sub> = +2.5V, V<sub>SD</sub> = +2.5V, V<sub>TM</sub> = +3.3V, T\_A = +25^{\circ}\text{C}.) (Note 2)

| PARAMETER                                      | SYMBOL               | CONDITIONS                                                       | MIN                        | TYP | МАХ                       | UNITS |

|------------------------------------------------|----------------------|------------------------------------------------------------------|----------------------------|-----|---------------------------|-------|

|                                                |                      | $V_{SD} < 2.4V$                                                  | 0.8 x                      |     |                           |       |

| Input High Voltage                             | VIH                  |                                                                  | V <sub>SD</sub>            |     |                           | V     |

|                                                |                      | $V_{SD} \ge 2.4V$                                                | 0.625 x<br>V <sub>SD</sub> |     |                           |       |

|                                                |                      | $V_{SD} < 2.4V$                                                  |                            |     | 0.2 x<br>V <sub>SD</sub>  |       |

| Input Low Voltage                              | VIL                  | $V_{SD} \ge 2.4V$                                                |                            |     | 0.25 x<br>V <sub>SD</sub> | V     |

| USB INTERFACE                                  |                      |                                                                  |                            |     |                           |       |

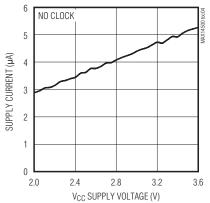

| On-Resistance                                  | RON                  | $V_{CD_{-}} = 0$ or $V_{TM}$ , switch closed                     |                            | 5   |                           | Ω     |

| On-Resistance Flatness                         | Ronflat              | $V_{CD_{}} = 0 \text{ to } 3.3 \text{V}, V_{TM} = +3.3 \text{V}$ |                            | 2   |                           | Ω     |

| On-Capacitance                                 | C <sub>ON_USB</sub>  | Switch closed, measured from CD+ and CD-                         |                            | 12  |                           | pF    |

| Off-Capacitance                                | C <sub>OFF_USB</sub> | Switch open, measured from CD+, CD-,<br>HD+, HD-                 |                            | 6   |                           | pF    |

| AC CHARACTERISTICS (Note 6)                    |                      |                                                                  |                            |     |                           |       |

| SD CARD CLOCK TIMING (CCLK                     | _), DEFAUL1          | ۲ SPEED (Figure 5a)                                              |                            |     |                           |       |

| Clock Low Time                                 | twL                  | $C_L = 10 pF$                                                    | 19                         |     |                           | ns    |

| Clock High Time                                | twH                  | $C_L = 10 pF$                                                    | 19                         |     |                           | ns    |

| Clock Rise Time                                | t <sub>TLH</sub>     | $C_L = 10 pF$                                                    |                            |     | 10                        | ns    |

| Clock Fall Time                                | t <sub>THL</sub>     | $C_L = 10 pF$                                                    |                            |     | 10                        | ns    |

| SD CARD CLOCK TIMING (CCLK                     | (_), HI-SPEED        | D (Figure 5b)                                                    |                            |     |                           |       |

| Clock Low Time                                 | twL                  | $C_L = 40 pF$                                                    | 7                          |     |                           | ns    |

| Clock High Time                                | twH                  | $C_L = 40 pF$                                                    | 7                          |     |                           | ns    |

| Clock Rise Time                                | t <sub>TLH</sub>     | $C_L = 40 pF$                                                    |                            |     | 3                         | ns    |

| Clock Fall Time                                | t <sub>THL</sub>     | $C_L = 40 pF$                                                    |                            |     | 3                         | ns    |

| SD CARD COMMAND TIMING (C                      | CMD1, CCMD           | 02) (Figure 5b)                                                  |                            |     |                           |       |

| Input Setup Time                               | tisu                 |                                                                  | 5                          |     |                           | ns    |

| Input Hold Time                                | t <sub>IH</sub>      |                                                                  | 2                          |     |                           | ns    |

| Output Delay Time During Data<br>Transfer Mode | todly                |                                                                  |                            |     | 14                        | ns    |

| Output Hold Time                               | tон                  |                                                                  | 2.5                        |     |                           | ns    |

| I <sup>2</sup> C CHARACTERISTICS               |                      |                                                                  |                            |     |                           |       |

| SCL Clock Frequency                            | fSCL                 |                                                                  |                            |     | 400                       | kHz   |

| SDA, SCL Capacitance                           | CIO_I2C              |                                                                  |                            | 5   |                           | pF    |

| SDA Output Fall Time                           | toF_I2C              |                                                                  |                            |     | 250                       | ns    |

| Hold Time After Repeated START                 | <sup>t</sup> hd,sta  |                                                                  | 0.6                        |     |                           | μs    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{CC} = +2.4V \text{ to } +3.6V, V_{SD} = +2.4V \text{ to } +3.6V, V_{IO} = +1.5V \text{ to } +3.6V, V_{TM} = +2.91V \text{ to } +3.4V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$ noted. Typical values are at V<sub>CC</sub> = +3.3V, V<sub>IO</sub> = +2.5V, V<sub>SD</sub> = +2.5V, V<sub>TM</sub> = +3.3V, T\_A = +25^{\circ}\text{C}.) (Note 2)

| PARAMETER                               | SYMBOL              | CONDITIONS | MIN | ТҮР | MAX | UNITS |

|-----------------------------------------|---------------------|------------|-----|-----|-----|-------|

| Clock Low Period                        | tLOW_I2C            |            | 1.3 |     |     | μs    |

| Clock High Period                       | thigh_i2C           |            | 0.6 |     |     | μs    |

| Setup Time for Repeated START           | tsu,sta             |            | 0.6 |     |     | μs    |

| Hold Time for Data                      | <sup>t</sup> hd,dat |            |     | 0   | 0.9 | μs    |

| Setup Time for Data                     | tsu,dat             |            | 100 |     |     | ns    |

| SDA/SCL Input Fall Time                 | tF_I2C              |            |     |     | 300 | ns    |

| SDA/SCL Rise Time                       | t <sub>R_I2C</sub>  |            |     |     | 300 | ns    |

| Setup Time for STOP                     | tsu,sto             |            | 0.6 |     |     | μs    |

| Bus Free Time Between STOP<br>and START | tBUF                |            | 1.3 |     |     | μs    |

### **USB HI-SPEED SOURCE ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.4V \text{ to } +3.6V, V_{SD} = +2.4V \text{ to } +3.6V, V_{IO} = +1.5V \text{ to } +3.6V, V_{TM} = +2.91V \text{ to } +3.4V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$

| PARAMETER                                                       | SYMBOL              | CONDITIONS                                 | MIN                                                                | ТҮР | MAX  | UNITS |  |  |

|-----------------------------------------------------------------|---------------------|--------------------------------------------|--------------------------------------------------------------------|-----|------|-------|--|--|

| DC CHARACTERISTICS                                              |                     |                                            |                                                                    |     |      |       |  |  |

| Hi-Speed Squelch Detection<br>Threshold (Diff Signal Amplitude) | V <sub>HSSQ</sub>   | (Note 6)                                   | 100                                                                |     | 150  | mV    |  |  |

| Hi-Speed Differential Input<br>Signaling Levels                 | VIL                 | Specified by Hi-Speed receive eye diagram  |                                                                    |     |      |       |  |  |

| Hi-Speed Data Signaling<br>Common-Mode Voltage Range            | SCM                 | (Note 6)                                   | -50                                                                |     | +500 | mV    |  |  |

| Hi-Speed Idle Level                                             | V <sub>HSOI</sub>   |                                            | -10                                                                |     | +10  | mV    |  |  |

| Hi-Speed Data Signaling High                                    | V <sub>HSOH</sub>   |                                            | 360                                                                |     | 440  | mV    |  |  |

| Hi-Speed Data Signaling Low                                     | VHSOL               |                                            | -10                                                                |     | +10  | mV    |  |  |

| Chirp J Level (Differential<br>Voltage)                         | V <sub>CHIRPJ</sub> |                                            | 700                                                                |     | 1100 | mV    |  |  |

| Chirp K Level (Differential<br>Voltage)                         | VCHIRPK             |                                            | -900                                                               |     | -500 | mV    |  |  |

| Termination Voltage (Hi-Speed)                                  | VHSTERM             |                                            | -10                                                                |     | +10  | mV    |  |  |

| AC CHARACTERISTICS                                              |                     |                                            |                                                                    |     |      |       |  |  |

| Rise Time                                                       | tHSR                | (Note 6)                                   | 500                                                                |     |      | ps    |  |  |

| Fall Time                                                       | tHSF                | (Note 6)                                   | 500                                                                |     |      | ps    |  |  |

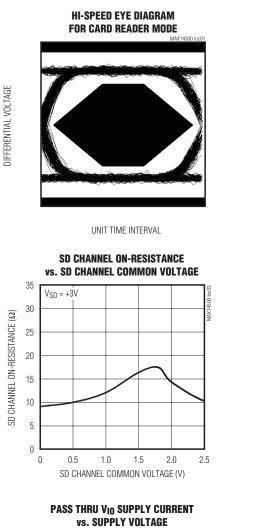

| Driver Waveform Requirements                                    |                     | Specified by Hi-Speed transmit eye diagram | See the <i>Typical Operating</i> Characteristics section           |     |      |       |  |  |

| Driver-Output Resistance                                        | Z <sub>HSDRV</sub>  |                                            | 40.5                                                               |     | 49.5 | Ω     |  |  |

| Source Jitter Total (Including<br>Frequency Tolerance)          |                     | Specified by Hi-Speed transmit eye diagram | See the <i>Typical Operating</i><br><i>Characteristics</i> section |     |      |       |  |  |

### **USB FULL-SPEED SOURCE ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +2.4V \text{ to } +3.6V, V_{SD} = +2.4V \text{ to } +3.6V, V_{IO} = +1.5V \text{ to } +3.6V, V_{TM} = +2.91V \text{ to } +3.4V, T_A = -40^{\circ}\text{C} \text{ to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$ noted. Typical values are at V<sub>CC</sub> = +3.3V, V<sub>IO</sub> = +2.5V, V<sub>SD</sub> = +2.5V, V<sub>TM</sub> = +3.3V, T\_A = +25^{\circ}\text{C}.) (Note 2)

| PARAMETER                                                                   | SYMBOL            | CONDITIONS                            | MIN    | ТҮР             | MAX    | UNITS |

|-----------------------------------------------------------------------------|-------------------|---------------------------------------|--------|-----------------|--------|-------|

| DC CHARACTERISTICS                                                          |                   | •                                     |        |                 |        | •     |

| SE Receiver Input High                                                      | VIH               |                                       | 2.0    |                 |        | V     |

| SE Receiver Input Low                                                       | VIL               |                                       |        |                 | 0.8    | V     |

| Differential Common-Mode<br>Voltage                                         | V <sub>CM</sub>   |                                       | 0.8    |                 | 2.0    | V     |

| Receiver Differential Input<br>Sensitivity                                  | V <sub>DI</sub>   |                                       | 0.2    |                 |        | V     |

| Transmitter High                                                            | VOH               | $R_L = 15k\Omega$ connected to GND    | 2.8    |                 | 3.6    | V     |

| Transmitter Low                                                             | VOL               | $R_L = 1.5 k\Omega$ connected to 3.3V | 0      |                 | 0.3    | V     |

| Transmitter Output Signal<br>Crossover Voltage                              | VCRS              | (Note 6)                              | 1.3    |                 | 2.0    | V     |

| Bus Pullup Resistor on Upstream<br>Facing Port (Idle Bus)                   | R <sub>PUI</sub>  |                                       | 0.900  | 1.25            | 1.575  | kΩ    |

| Bus Pullup Resistor on Upstream<br>Facing Port (Upstream Port<br>Receiving) | Rpua              |                                       | 1.425  | 2.5             | 3.090  | kΩ    |

| Input Impedance                                                             | ZINP              |                                       | 300    |                 |        | kΩ    |

| Termination Voltage for Upstream<br>Facing Port Pullup (RPU)                | VTERM             |                                       |        | V <sub>TM</sub> |        | V     |

| AC CHARACTERISTICS                                                          |                   | •                                     |        |                 |        | •     |

| Rise Time                                                                   | tFR               |                                       | 4      |                 | 20     | ns    |

| Fall Time                                                                   | tFF               |                                       | 4      |                 | 20     | ns    |

| Differential Rise and Fall Time<br>Matching                                 | <sup>t</sup> FRFM | (Note 6)                              | 90     |                 | 111.11 | %     |

| Full-Speed Data Rate                                                        | <b>t</b> FDRATHS  |                                       | 11.994 |                 | 12.030 | Mbps  |

Note 2: All parameters are tested at  $T_A = +25^{\circ}C$ . Specifications over temperature are guaranteed by design.

Note 3: On-resistance is measured by applying voltage and current on the SD card interface (CCLK1, CCMD1, CDAT1\_[3:0], CCLK2, CCMD2, CDAT2\_[3:0]).

Note 4: Off-capacitance measured with SD switch open (CCLK1, HCLK1, CCMD1, HCMD1, CDAT1\_[3:0], HDAT1\_[3:0], CCLK2, HCLK2, CCMD2, HCMD2, CDAT2\_[3:0], HDAT2\_[3:0]).

Note 5: On-capacitance measured on SD card side (CCLK1, CCMD1, CDAT1\_[3:0], CCLK2, CCMD2, CDAT2\_[3:0]).

Note 6: Specifications guaranteed by design.

### **Typical Operating Characteristics**

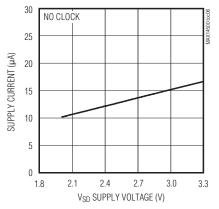

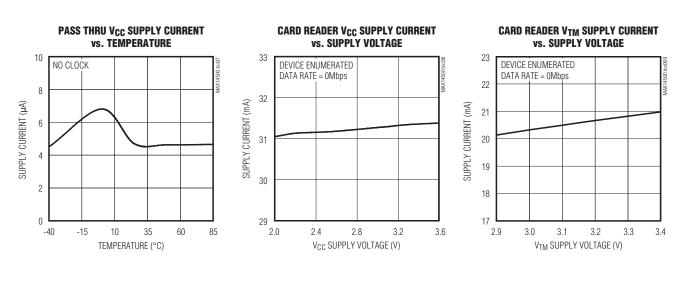

$(V_{CC} = +3.3V, V_{IO} = +2.5V, V_{SD} = +2.5V, V_{TM} = +3.3V, T_A = +25^{\circ}C$ , unless otherwise noted.)

PASS THRU V<sub>CC</sub> SUPPLY CURRENT vs. SUPPLY VOLTAGE

PASS THRU V<sub>SD</sub> SUPPLY CURRENT vs. SUPPLY VOLTAGE

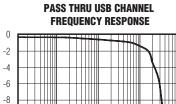

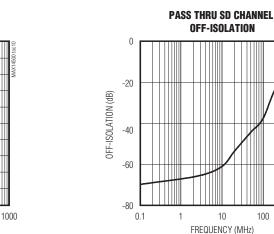

### **Typical Operating Characteristics (continued)**

$(V_{CC} = +3.3V, V_{IO} = +2.5V, V_{SD} = +2.5V, V_{TM} = +3.3V, T_A = +25^{\circ}C$ , unless otherwise noted.)

10

FREQUENCY (MHz)

100

ON-LOSS (dB)

-10

-12 -14

-16 -18 -20

0.1

1

10

100

1000

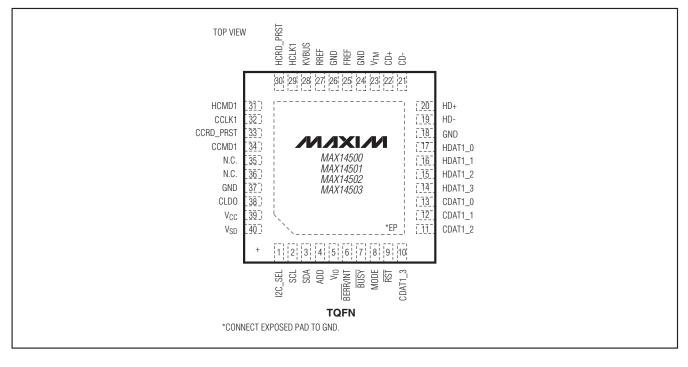

### Pin Description

| P          | IN      |          |                                                                                                                                                                                                                                                                                                                         |

|------------|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN       | WLP     | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                |

| INPUTS/OUT | PUTS    |          |                                                                                                                                                                                                                                                                                                                         |

| 1          | C4      | I2C_SEL  | I <sup>2</sup> C Select Input. I2C_SEL must be connected to $V_{IO}$ or GND at power-up. Drive I2C_SEL low to disable I <sup>2</sup> C control and drive I2C_SEL high to enable I <sup>2</sup> C control.                                                                                                               |

| 2          | A2      | SCL      | I <sup>2</sup> C Serial-Clock Input. SCL is +3.6V tolerant and the high threshold is set by $V_{IO}$ . If the I <sup>2</sup> C interface is not used, connect SCL to GND.                                                                                                                                               |

| 3          | B4      | SDA      | I <sup>2</sup> C Serial-Data I/O. SDA is +3.6V tolerant and the high threshold is set by $V_{IO}$ . If the I <sup>2</sup> C interface is not used, connect SDA to GND.                                                                                                                                                  |

| 4          | A3      | ADD      | I <sup>2</sup> C Address Selection Input. Connect ADD to V <sub>IO</sub> or GND to select between two I <sup>2</sup> C slave addresses: (GND = 1110 000Xb and V <sub>IO</sub> = 1110 001Xb).                                                                                                                            |

| 6          | B6      | BERR/INT | Card Reader Error/Interrupt Output. BERR/INT becomes BERR for simple control and INT for I <sup>2</sup> C control. BERR/INT goes low to indicate an error in Card Reader mode during simple control and asserts for enabled interrupts during I <sup>2</sup> C control.                                                 |

| 7          | A7      | BUSY     | Busy Output. BUSY asserts low to indicate device is in Card Reader mode.                                                                                                                                                                                                                                                |

| 8          | C6      | MODE     | Card Reader/Pass Thru Mode Select Input. MODE is only active during simple control. Drive MODE low to enable Pass Thru mode and drive MODE high to enable Card Reader mode. For I <sup>2</sup> C control, MODE must be connected to GND.                                                                                |

| 9          | B7      | RST      | Reset Input. Drive $\overline{\text{RST}}$ low to reset the internal registers to default values and put all outputs in high impedance. Connect $\overline{\text{RST}}$ to V <sub>IO</sub> for normal operation.                                                                                                        |

| 25         | E6      | FREF     | Frequency Input. FREF is the clock input (12MHz/13MHz/19.2MHz/26MHz) for the internal logic and USB PHY. FREF can accept a square-wave or sine-wave clock. An internal clock squaring circuit can be enabled or disabled through I <sup>2</sup> C. In simple control, the internal clock squarer is enabled by default. |

| 27         | F5      | RREF     | Reference Resistor. Connect a Bias Resistor 6.19k $\Omega \pm 1\%$ from RREF to GND.                                                                                                                                                                                                                                    |

| USB INTERF | ACE     |          |                                                                                                                                                                                                                                                                                                                         |

| 22         | G7      | CD+      | USB Analog Switch/Hi-Speed USB Transceiver. CD+ connects to D+ on the USB connector.                                                                                                                                                                                                                                    |

| 21         | F7      | CD-      | USB Analog Switch/Hi-Speed USB Transceiver. CD- connects to D- on the USB connector.                                                                                                                                                                                                                                    |

| 20         | G8      | HD+      | USB Analog Switch. HD+ connects to D+ on the host side.                                                                                                                                                                                                                                                                 |

| 19         | F8      | HD-      | USB Analog Switch. HD- connects to D- on the host side.                                                                                                                                                                                                                                                                 |

| 28         | E5      | KVBUS    | USB Bus Power-Supply Detection Input. Connect a resistor-divider between USB VBUS, KVBUS, and GND.                                                                                                                                                                                                                      |

| SD CARD IN | TERFACE |          |                                                                                                                                                                                                                                                                                                                         |

| 13         | C8      | CDAT1_0  | SD Card 1 Data Bus Analog Switch/Card Reader Interface. CDAT1_0 connects to DAT0 on the SD card.                                                                                                                                                                                                                        |

| 12         | B8      | CDAT1_1  | SD Data Card 1 Bus Analog Switch/Card Reader Interface. CDAT1_1 connects to DAT1 on the SD card.                                                                                                                                                                                                                        |

| 11         | C7      | CDAT1_2  | SD Data Card 1 Bus Analog Switch/Card Reader Interface. CDAT1_2 connects to DAT2 on the SD card.                                                                                                                                                                                                                        |

| L          | •       |          |                                                                                                                                                                                                                                                                                                                         |

### Pin Description (continued)

| Р    | PIN |           |                                                                                                                                                                         |

|------|-----|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TQFN | WLP | NAME      | FUNCTION                                                                                                                                                                |

| 10   | A8  | CDAT1_3   | SD Card 1 Data Bus Analog Switch/Card Reader Interface. CDAT1_3 connects to DAT3 on the SD card.                                                                        |

| 34   | E2  | CCMD1     | SD Card 1 Command Analog Switch/Card Reader Interface. CCMD1 connects to CMD on the SD card.                                                                            |

| 32   | E3  | CCLK1     | SD Card 1 Clock Analog Switch/Card Reader Interface. CCLK1 connects to CLK on the SD card.                                                                              |

| 33   | F1  | CCRD_PRST | SD Card 1 Analog Switch for Card Present Detection. CCRD_PRST is the card detection line to the SD socket. When in Pass Thru mode, CCRD_PRST is connected to HCRD_PRST. |

| 17   | D7  | HDAT1_0   | SD Card 1 Data Bus Analog Switch. HDAT1_0 connects to DAT0 on the SD port of the host $\mu$ P.                                                                          |

| 16   | D8  | HDAT1_1   | SD Card 1 Data Bus Analog Switch. HDAT1_1 connects to DAT1 on the SD port of the host $\mu P.$                                                                          |

| 15   | D6  | HDAT1_2   | SD Card 1 Data Bus Analog Switch. HDAT1_2 connects to DAT2 on the SD port of the host $\mu$ P.                                                                          |

| 14   | D5  | HDAT1_3   | SD Card 1 Data Bus Analog Switch. HDAT1_3 connects to DAT3 on the SD port of the host $\mu P.$                                                                          |

| 31   | G1  | HCMD1     | SD Card 1 Command Analog Switch. HCMD1 connects to CMD on the SD port of the host $\mu P.$                                                                              |

| 29   | G2  | HCLK1     | SD Card 1 Clock Analog Switch. HCLK1 connects to CLK on the SD port of the host $\mu$ P.                                                                                |

| 30   | F2  | HCRD_PRST | SD Card 1 Analog Switch for Card Present Detection. HCRD_PRST is connected to CCRD_PRST in Pass Thru mode.                                                              |

| _    | D2  | CDAT2_0   | SD Card 2 Data Bus Analog Switch/Card Reader Interface. CDAT2_0 connects to DAT0 on the SD card.                                                                        |

| _    | D1  | CDAT2_1   | SD Card 2 Data Bus Analog Switch/Card Reader Interface. CDAT2_1 connects to DAT1 on the SD card.                                                                        |

| _    | B5  | CDAT2_2   | SD Card 2 Data Bus Analog Switch/Card Reader Interface. CDAT2_2 connects to DAT2 on the SD card.                                                                        |

| _    | A5  | CDAT2_3   | SD Card 2 Data Bus Analog Switch/Card Reader Interface. CDAT2_3 connects to DAT3 on the SD card.                                                                        |

| _    | F4  | CCMD2     | SD Card 2 Command Analog Switch/Card Reader Interface. CCMD2 connects to CMD on the SD card.                                                                            |

| _    | F3  | CCLK2     | SD Card 2 Clock Analog Switch/Card Reader Interface. CCLK2 connects to CLK on the SD card.                                                                              |

| _    | D3  | HDAT2_0   | SD Card 2 Data Bus Analog Switch. HDAT2_0 connects to DAT0 on the SD port of the host $\mu P.$                                                                          |

| _    | E1  | HDAT2_1   | SD Card 2 Data Bus Analog Switch. HDAT2_1 connects to DAT1 on the SD port of the host $\mu$ P.                                                                          |

### Pin Description (continued)

| Р                 | PIN                       |                 | FUNCTION                                                                                                                                                                            |  |  |  |

|-------------------|---------------------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| TQFN              | WLP                       | NAME            | FUNCTION                                                                                                                                                                            |  |  |  |

|                   | C5                        | HDAT2_2         | SD Card 2 Data Bus Analog Switch. HDAT2_2 connects to DAT2 on the SD port of the host $\mu$ P.                                                                                      |  |  |  |

| _                 | A4                        | HDAT2_3         | SD Card 2 Data Bus Analog Switch. HDAT2_3 connects to DAT3 on the SD port of the host $\mu P.$                                                                                      |  |  |  |

| _                 | G4                        | HCMD2           | SD Card 2 Command Analog Switch. HCMD2 connects to CMD on the SD port of the host $\mu$ P.                                                                                          |  |  |  |

| _                 | G3                        | HCLK2           | SD Card 2 Clock Analog Switch. HCLK2 connects to CLK on the SD port of the host $\mu$ P.                                                                                            |  |  |  |

| POWER SUP         | PLY                       |                 |                                                                                                                                                                                     |  |  |  |

| 5                 | A6                        | V <sub>IO</sub> | I/O Logic-Level Translator Voltage. Bypass V <sub>IO</sub> to GND with a 0.1 $\mu F$ ceramic capacitor. V <sub>IO</sub> powers the logic inputs/outputs and I <sup>2</sup> C block. |  |  |  |

| 23                | F6                        | V <sub>TM</sub> | USB Analog Switch and Transceiver Power Supply. Bypass $V_{TM}$ to GND with a $0.1 \mu F$ ceramic capacitor.                                                                        |  |  |  |

| 38                | B1, B2                    | CLDO            | Bypass Capacitor for Internal +1.8V LDO. Connect a 1µF ceramic capacitor (X7R, X5R, or better) from CLDO to GND. CLDO must not be used to power external circuitry.                 |  |  |  |

| 39                | B3, C3                    | Vcc             | Digital Supply Voltage. Bypass V <sub>CC</sub> to GND with a $1\mu$ F ceramic capacitor (X7R, X5R, or better).                                                                      |  |  |  |

| 40                | A1                        | V <sub>SD</sub> | SD Card Voltage. Bypass $V_{SD}$ to GND with a $1\mu F$ ceramic capacitor (X7R, X5R, or better).                                                                                    |  |  |  |

| 18, 24, 26,<br>37 | C1, C2, E7,<br>E8, G5, G6 | GND             | Ground                                                                                                                                                                              |  |  |  |

| NO CONNEC         | TION                      |                 |                                                                                                                                                                                     |  |  |  |

| 35, 36            | D4, E4                    | N.C.            | No Connection. Connect N.C. to GND.                                                                                                                                                 |  |  |  |

| EXPOSED P         | AD                        |                 |                                                                                                                                                                                     |  |  |  |

| —                 |                           | EP              | Exposed Pad. Connect EP to GND. Do not use EP as the sole GND connection.                                                                                                           |  |  |  |

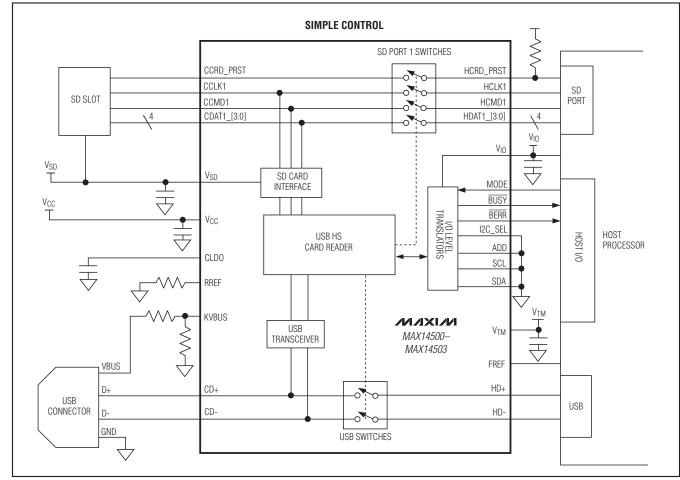

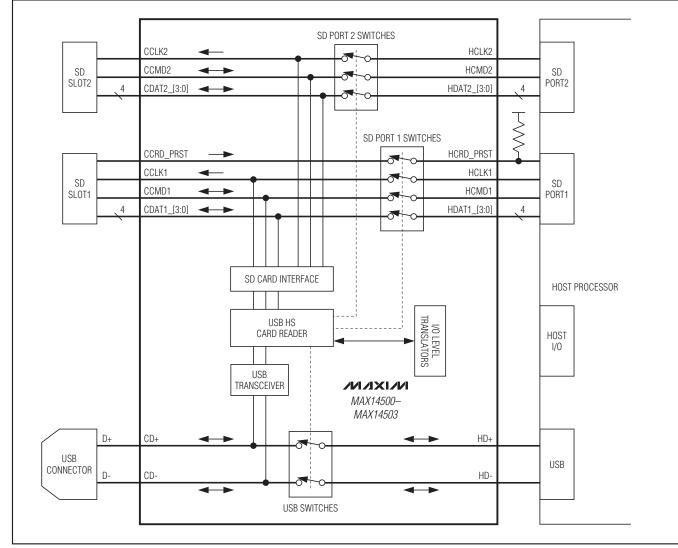

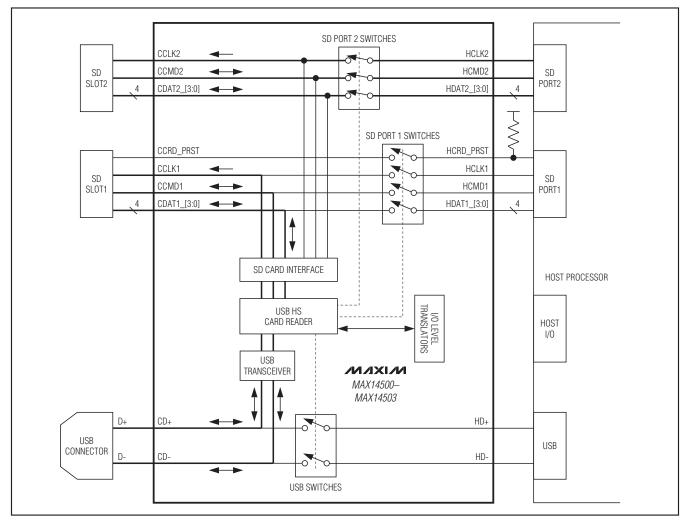

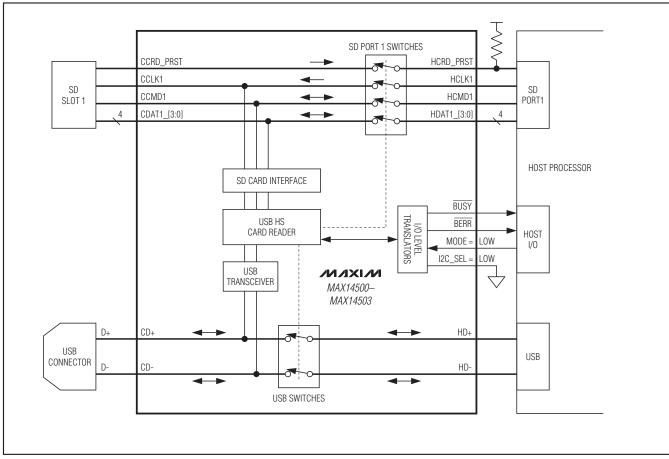

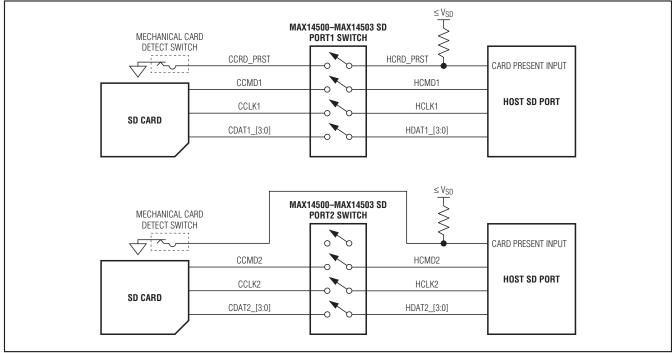

Figure 1. Typical Application Circuit for Simple Control Mode with One SD Card

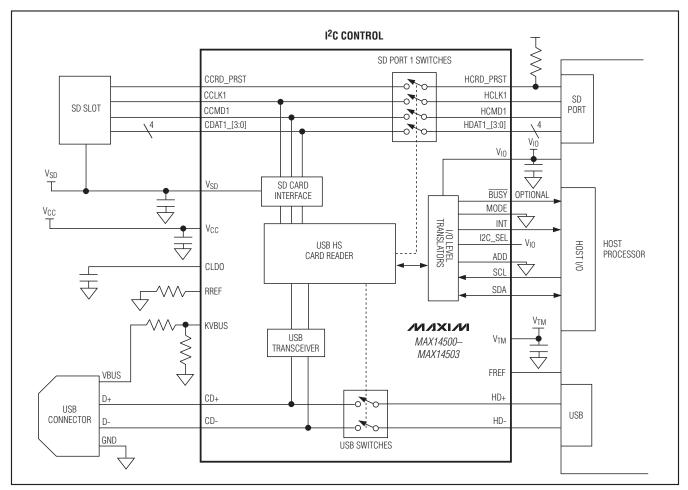

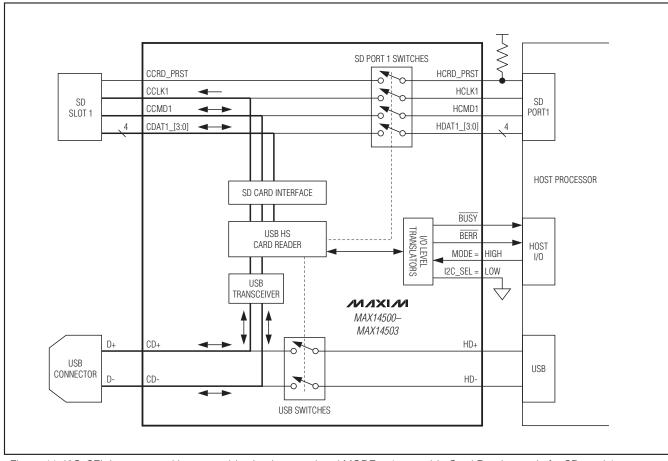

Figure 2. Typical Application Circuit for I<sup>2</sup>C Control Mode with One SD Card

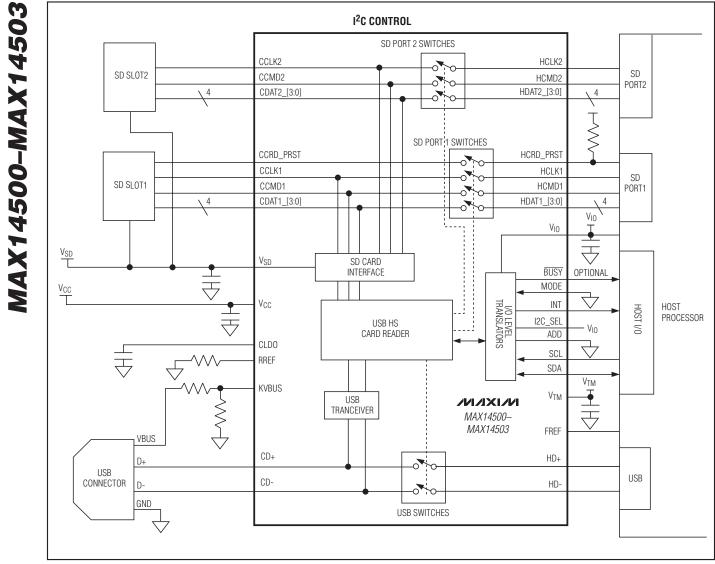

Figure 3. Typical Application Circuit for I<sup>2</sup>C Control Mode with Two SD Cards

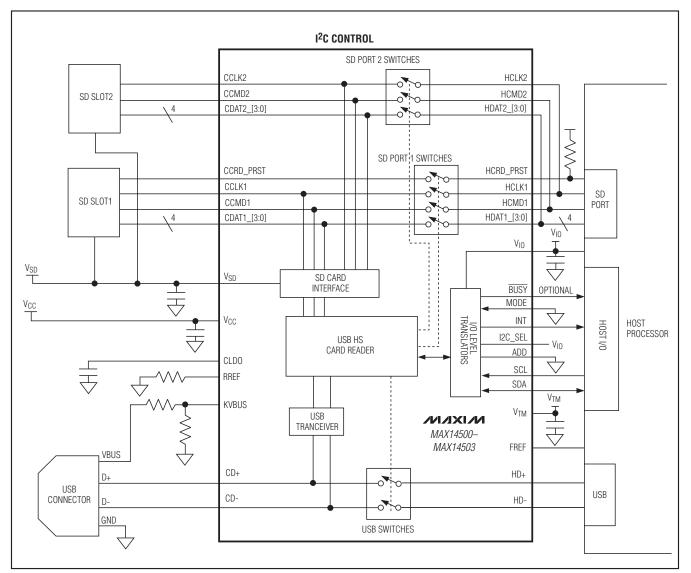

Figure 4. Typical Application Circuit for I<sup>2</sup>C Control Mode with One SD Port and Two SD Cards

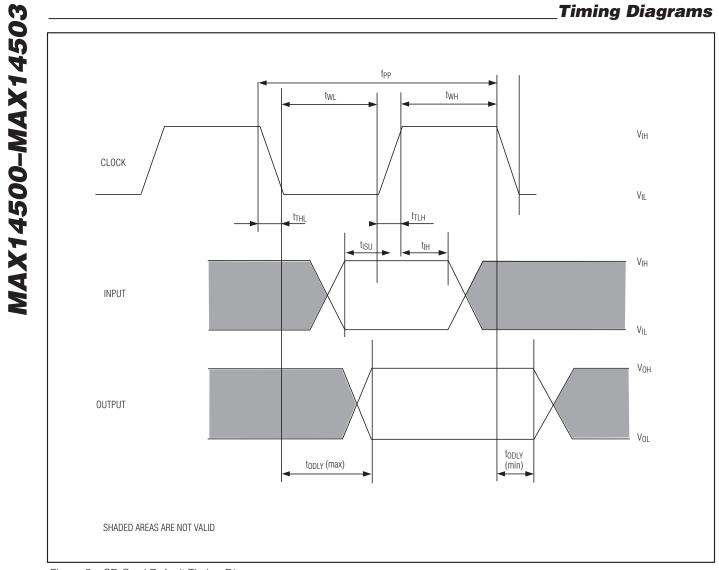

Figure 5a. SD Card Default Timing Diagram

### Timing Diagrams (continued)

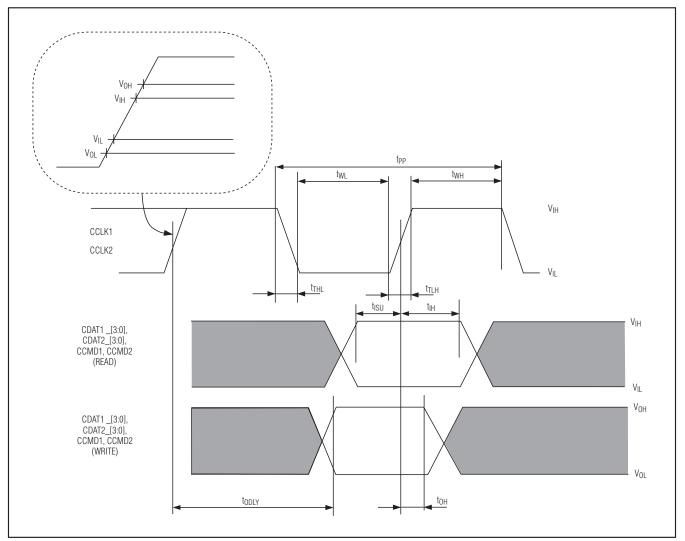

Figure 5b. SD Card Hi-Speed Timing Diagram

MAX14500-MAX14503

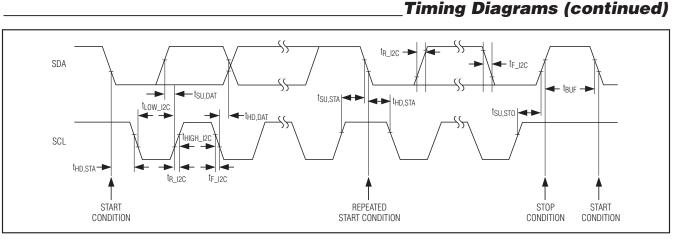

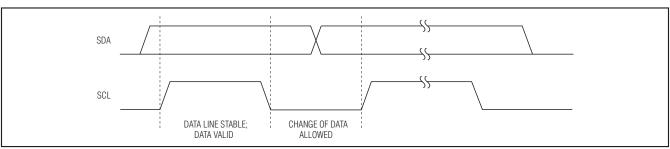

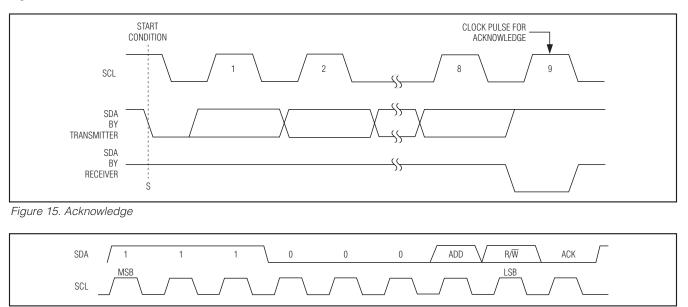

Figure 6. I<sup>2</sup>C Timing Diagram

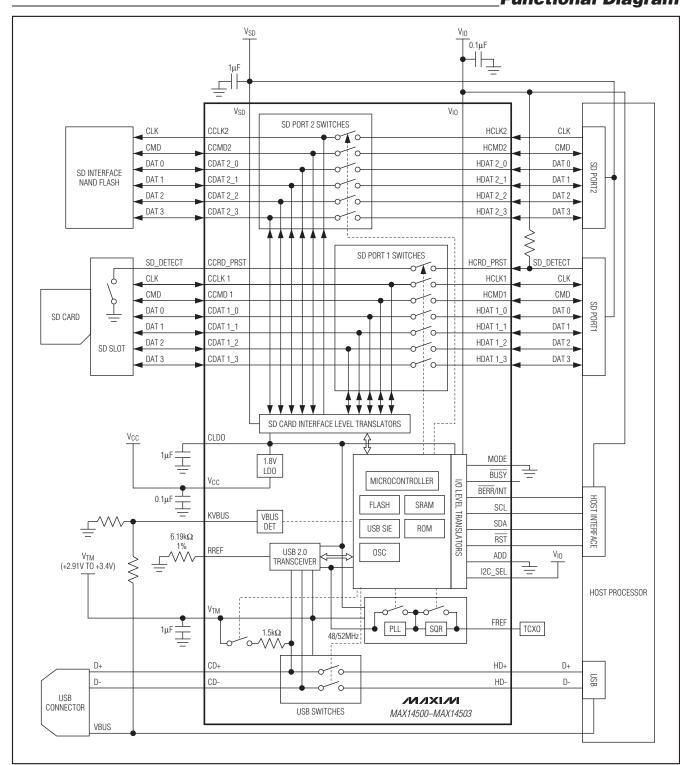

#### **Detailed Description**

The MAX14500-MAX14503 can be added to devices that have an SD card slot and a USB full-speed port (12Mbps) to provide a Hi-Speed USB path to an SD card bypassing the host microprocessor (µP), allowing for faster SD card transfers (Figures 1-4). Without the MAX14500-MAX14503, a host µP with a full-speed USB port moves data between an SD card and a host PC at 12Mbps when transferring data from an SD card through USB. The host µP has additional overhead because it has to accept data from the SD cards, process the data by putting it in USB format, and then transfer the data through the USB port. The MAX14500-MAX14503 create an alternate path from the SD card to USB, providing USB Hi-Speed capability. By bypassing the host µP using the MAX14500-MAX14503, SD card read and write operations are not limited by host uP overhead and USB full-speed data rates.

The MAX14500–MAX14503 operate in Pass Thru and Card Reader mode. In Pass Thru mode, the MAX14500–MAX14503 are transparent to the host  $\mu$ P. All read and write operations pass from the host  $\mu$ P SD port to the SD card without modification. All of the features of the original device are intact and there is no need to change firmware in the host  $\mu$ P. In Card Reader mode, the SD card is connected to the PC with the internal USB Hi-Speed card reader, bypassing the host  $\mu$ P.

The MAX14500–MAX14503 can be controlled in two ways. The simple control method uses a single output from a  $\mu$ P or ASIC to select Pass Thru or Card Reader mode. Only one SD card can be used as a Hi-Speed USB card reader in simple control. I<sup>2</sup>C control allows more configuration options and provides status information along with error conditions and additional interrupts. Two SD cards can be connected and each set of SD port switches can be controlled independently (two SD port version under I<sup>2</sup>C control). The state of I2C\_SEL must not change after VIO is applied.

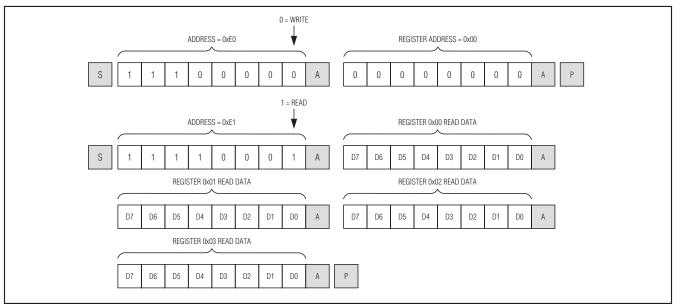

With I<sup>2</sup>C control, the I<sup>2</sup>C bus is used to read and write to internal registers for configuration, error checking, control, and status reporting. The control and configuration registers have various functions including wakeup, SD card selection, interrupt enable, and SD switch settings. The status registers give the status of errors, SD card detection, power supplies, and interrupts. Putting the MAX14500-MAX14503 to sleep puts the device into Pass Thru mode. The state of SD port switches for card 1 and card 2 can be changed while in Pass Thru. Some I<sup>2</sup>C commands are executed upon waking up or entering Card Reader mode. For register settings that involve Card Reader mode, (when in Sleep mode), programming the I<sup>2</sup>C registers changes the values, but the actions do not execute until the internal logic wakes up or Card Reader mode is entered. The register map indicates when register bit changes take effect.

### Table 1. Power-Up Default Mini Register Map for Configuration Registers

| REGISTER NAME                            | REGISTER<br>ADDRESS<br>(hex) | POWER-UP VALUE<br>(hex) | POWER-UP DEFAULT SETTINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------------------------------------|------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Register<br>(CONTROL)            | 0x00                         | 0x18                    | SD2SW = 1, SD switch 2 is closed<br>SD1SW = 1, SD switch 1 is closed<br>MODE[1:0] = 00, Card Reader mode is not active<br>WAKEUP = 0, shutdown                                                                                                                                                                                                                                                                                                                                                                   |

| Configuration<br>Register 1<br>(CONFIG1) | 0x01                         | 0x00                    | SD2ONEBIT = 0, SD2 bus in 4-bit data mode<br>SD1ONEBIT = 0, SD1 bus in 4-bit data mode<br>INTPULSE = 0, INT stays asserted until status register is read<br>INTACTHI = 0, INT asserts active low                                                                                                                                                                                                                                                                                                                 |

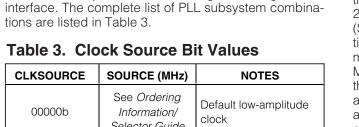

| Configuration<br>Register 2<br>(CONFIG2) | 0x02                         | 0x00                    | CLKSOURCE = 00000, default clock input<br>FORCEFS = 0, USB Hi-Speed                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Configuration<br>Register 3<br>(CONFIG3) | 0x03                         | 0x00                    | SD2MAXCLK = 0000, default clock (base SD clock)<br>SD1MAXCLK = 0000, default clock (base SD clock)                                                                                                                                                                                                                                                                                                                                                                                                               |

| Interrupt Enable<br>Register 1<br>(IE1)  | 0x04                         | 0x00                    | $\begin{array}{l} \text{USBFS} = 0, \mbox{ disable INT for full-speed status change} \\ \text{USBSR} = 0, \mbox{ disable INT for suspend/resume status change} \\ \text{VTM} = 0, \mbox{ disable INT for V_{TM} status change} \\ \text{VSD} = 0, \mbox{ disable INT for V_{SD} status change} \\ \text{KVBUS} = 0, \mbox{ disable INT for VBUS status change} \\ \text{BSY} = 0, \mbox{ disable INT for BUSY status change} \\ \text{SDSTAT} = 0, \mbox{ disable INT for SD card status change} \\ \end{array}$ |

| Interrupt Enable<br>Register 2<br>(IE2)  | 0x05                         | 0x00                    | FWUPD = 0, disable INT for firmware update status change                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| USB Vendor ID<br>High Byte<br>(USBVIDH)  | 0x06                         | 0x00                    | If VID = 0x0000, 0x06BA is used during USB enumeration,<br>VID high byte = 0x06                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB Vendor ID<br>Low Byte<br>(USBVIDL)   | 0x07                         | 0x00                    | If VID = 0x0000, 0x06BA is used during USB enumeration,<br>VID low byte = 0xBA                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| USB Product ID<br>High Byte<br>(USBPIDH) | 0x08                         | 0x00                    | If PID = 0x0000, 0x38A4 is used during USB enumeration,<br>PID high byte = 0x38                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| USB Product ID<br>Low Byte<br>(USBPIDL)  | 0x09                         | 0x00                    | If PID = 0x0000, 0x38A4 is used during USB enumeration.<br>PID low byte = 0xA4                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Figure 7. Default Startup (Pass Thru Mode)

#### **Default Power-Up (Pass Thru Mode)**

In the default Pass Thru mode, the MAX14500– MAX14503 are transparent and the existing host functions (access to SD cards and USB) are preserved (Figure 7). The host  $\mu$ P reads and writes data to the SD card from the SD port, and can communicate to a PC through its existing full-speed USB port. All of the features of the original chipset are intact. The MAX14500– MAX14503 sleep when in Pass Thru mode (WAKEUP = 0), when the MODE input is low, or when the MODE bits [2:1] in control register (0x00) are set to Card Reader mode, not active. In Sleep mode, the internal microcontroller is turned off and current consumption is minimized. The settings for SD port switches for card 1 and card 2 are controlled by SD port switch bits [4:3] in the control register.

#### **Card Reader Mode**

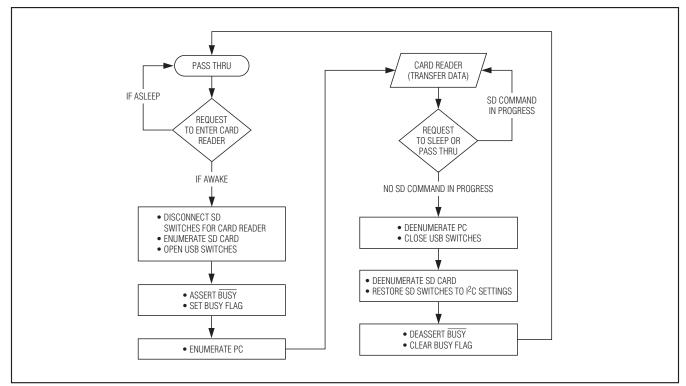

In Card Reader mode, the PC communicates with the SD card through USB with an internal Hi-Speed SD card reader, bypassing the host  $\mu$ P. Figure 8 shows card reader mode with SD card 1 connected to the PC with the internal card reader. The 40-pin TQFN can connect to a single SD card in Card Reader mode. With the 56-bump WLP operating under I<sup>2</sup>C control, either SD card can be selected for Card Reader mode.

Figure 8. Card Reader Mode. The USB port is connected to SD card 1. In the 2 port version, a second SD card (SD slot 2) can be independently connected and disconnected to the host  $\mu$ P.

When the card reader is initiated in the control register, the internal USB switch disconnects from the host  $\mu$ P USB port and connects to the internal USB Hi-Speed SD card reader unit. When the MAX14500–MAX14503 disconnect from the host to implement a stand-alone high-speed card reader, it simulates a disconnect on the host USB and SD ports to maintain data coherence. The SD connections are restored to the host  $\mu$ P by closing the analog switch connecting CCRD\_PRST to HCRD\_PRST.

Certain registers execute actions when entering Card Reader mode. These actions are only valid for Card Reader mode. Writing to these registers in Sleep mode, or when awake, updates the registers, but the action is carried out when Card Reader mode is activated for one of the SD cards (see the *Register Map* section).

When Card Reader mode is initially entered, the internal microcontroller enumerates with the PC to establish a high-speed USB mass storage device. No actions by the host  $\mu$ P are required for enumeration other than entering Card Reader mode. Once the USB-SD card connection is established, PC to SD card data transfer begins and various interrupts monitor the status the of Card Reader mode if enabled. The BSY flag is represented externally by the BUSY output and can be read serially through I<sup>2</sup>C. The BUSY output is always active. If the host  $\mu$ P requests Sleep mode in the middle of the data transfer, the MAX14500–MAX14503 do not complete the transfer, exit Card Reader mode, reconnect USB switches, and

MAX14500-MAX14503

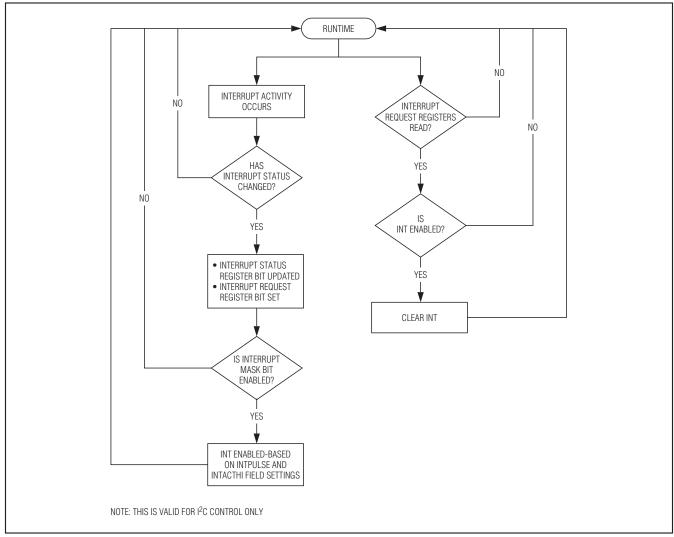

Figure 9. Card Reader Flow Chart

go to sleep. Because the  $\overline{\text{BUSY}}$  output (BSY bit in I<sup>2</sup>C) indicates Card Reader mode, the host  $\mu P$  may monitor this output after commanding a mode change to determine when the change takes place (Figure 9). If the host requests the other SD card to enter Card Reader mode, the busy flag deasserts and reasserts to let the host know that the change took place.

#### Simple Control (I2C\_SEL = Low)

The MAX14500–MAX14503 feature a very simple control scheme for entering Card Reader mode that requires a single logic (GPIO) from the host  $\mu$ P. The simple control may only be used with the single SD port versions. When I2C\_SEL is connected low at startup, the MODE input controls whether the device is in Pass Thru or Card Reader mode. Driving MODE low enables Pass Thru mode (Figure 10), and the host  $\mu$ P has a direct connection to the SD card and USB connector through internal analog switches. Driving MODE high enables Card Reader mode between SD card 1 and the PC through the USB connector (Figure 11). BERR/INT functions as the bridge error output BERR that asserts for card reader errors. Interrupts are not enabled, the clock source is set to the default as defined by the part number, and the BERR and BUSY outputs are active. Upon MODE transitioning high, SD card 1 connects to the USB connector in Card Reader mode and BUSY asserts low. The BUSY output indicates that the device is in Card Reader mode. BUSY may be important to the host  $\mu$ P, as the time to complete enumeration/de-enumeration may take a long time (> 100ms).

#### I<sup>2</sup>C Control (I2C\_SEL = High)

The MAX14500–MAX14503 feature I<sup>2</sup>C control that allows access to internal registers for complete control over configuration, SD port analog switches, interrupts, clock configuration, advanced power-on states, and error status. I<sup>2</sup>C control uses I<sup>2</sup>C to serially program the MAX14500–MAX14503 to be in Card Reader or Pass Thru mode, and allows either SD card to be connected in Card Reader mode. While a SD card is connected in Card Reader mode, the other SD port analog switches can be independently controlled serially through I<sup>2</sup>C. Using the I<sup>2</sup>C bus to put the device to sleep minimizes the supply current while maintaining control over the SD port switches.

Figure 10. I2C\_SEL Connected Low to Enable Simple Control and MODE = 0 to Enable Pass Thru

#### **Control Register (0x00)**

The control register controls the settings of SD port analog switches, Card Reader mode, and sleep (Table 2.) The state of the SD port analog switches can be changed when the device is in Sleep mode or in Card Reader mode, and actions are executed immediately. If SD card 1 is connected to the PC through USB in Card Reader mode, the state of the SD port 1 switches are ignored, but the SD port 2 switches can still be controlled through the Control register. Likewise, if SD card 2 is connected to the USB connector in Card Reader mode, the state of the SD port 2 switches are ignored, but the SD port 1 switches can still be controlled through the Control register. Changing the card reader bits in Sleep mode does not cause the device to enter Card Reader mode. Under this condition, the MAX14500-MAX14503 enter Card Reader mode upon waking up.

#### **Configuration Registers**

The MAX14500–MAX14503 have three configuration registers (CONFIG1 = 0x01, CONFIG2 = 0x02, CONFIG3 = 0x03). The configuration registers control the SD bus bit data mode, interrupt polarity, interrupt clearance, clock configuration, SD clock, and USB speed for Card Reader mode. The default settings are shown in the *Register Map* section.

#### Interrupts (INT)

All interrupts are masked in the default reset state. There are two interrupt enable registers (IE1 = 0x04, IE2 = 0x05) and two interrupt request registers (IRQ1 = 0x10, IRQ2 = 0x11). The BERR/INT output functions as the bridge error output BERR in simple control and functions as an interrupt INT in I<sup>2</sup>C control. The polarity of INT and how INT is asserted can be programmed in CONFIG1. The INT output asserts for enabled interrupts and errors in Card Reader mode. The polarity of INT can be active-high or active-low, and INT can be pro-

Table 2. Control Register (0x00)

| BIT   | DESCRIPTION                                                                                                                                                                                                              | VALUE  | FUNCTION                                                                    | DEFAULT |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------|---------|

| [7:5] | RESERVED                                                                                                                                                                                                                 | 000    | Set these bits to 0.                                                        | 000     |

| 4     | <b>SD PORT 2 ANALOG SWITCHES</b><br>SD Port 2 is a set of six analog switches connecting the SD port to the<br>SD card. This set contains: clock (CCLK2), command (CCMD2), and                                           | 0      | Analog switches are open,<br>disconnecting the SD port<br>from the SD card. | 1       |

| 4     | four data lines (CDAT2_[3:0]). The card-present line is not available for this port. This setting is ignored when Card Reader mode is enabled for this port.                                                             | 1      | Analog switches are<br>closed, connecting the SD<br>port to the SD card.    |         |

| 3     | <b>SD PORT 1 ANALOG SWITCHES</b><br>SD Port 1 is a set of seven analog switches connecting the SD port to<br>the SD card. This set contains: card-present (CCRD_PRST), clock                                             | 0      | Analog switches are open,<br>disconnecting the SD port<br>from the SD card. | 1       |

|       | (CCLK1), command (CCMD1), and four data lines (CDAT1_[3:0]). The difference between Port 1 and Port 2 is the card-present line. This setting is ignored when Card Reader mode is enabled for this port.                  | 1      | Analog switches are<br>closed, connecting the SD<br>port to the SD card.    |         |

|       | CARD READER MODE                                                                                                                                                                                                         | 00, 11 | Card Reader mode not active.                                                |         |

| [2:1] | Changing these bits in Sleep mode does not execute the action until the host $\mu$ P wakes up the MAX14500–MAX14503.                                                                                                     | 01     | Card Reader mode active:<br>Connects to SD card 1.                          | 00      |

|       |                                                                                                                                                                                                                          | 10     | Card Reader mode active:<br>Connects to SD card 2.                          |         |

| 0     | <b>WAKEUP</b><br>In Sleep mode, the MAX14500–MAX14503 are in Pass Thru mode. SD port switches are controlled by their respective bits. Entering Sleep mode reduces the supply current by turning off the internal logic. | 0      | Request internal logic to shut down.                                        | 0       |

|       | Request to shut down may be delayed due to USB and de-<br>enumeration.                                                                                                                                                   | 1      | Wake up internal logic.                                                     |         |

grammed to stay asserted until the status register is read, or stay asserted for 10ms. If INT is programmed to stay asserted, a read to the status register is required to clear INT. INT can be programmed to be active-high or active-low when I2C\_SEL is high (I<sup>2</sup>C control). INT is high impedance in Sleep mode (WAKEUP = 0), regardless of the INT polarity programmed in the I<sup>2</sup>C registers. Use a pullup or pulldown resistor for the desired inactive INT polarity state during Sleep mode.

#### Interrupt Masking

All interrupts are masked at power-up. While masked interrupts do not assert the INT output, they do register as changes in the interrupt request registers (IRQ1 and IRQ2). The status register (STATUS1 = 0x12) indicates the current state of the interrupt bits. If interrupts are masked, polling IRQ1 and IRQ2 indicate the fields with changes, and STATUS1 gives the current state. Reading the IRQ registers resets the interrupt request bits. If polling is used to read the device status, it is required to read both the status register and the interrupt request to check for state changes.

#### **USB** Interrupts

When enabled, the INT output asserts an interrupt for changes in the USB connection and if the operating system suspends the USB connection. VBUS is detected at the KVBUS input and changes in VBUS voltage can assert an interrupt when enabled.

#### **Power-Supply Interrupts**

The MAX14500–MAX14503 feature many advanced power-saving modes. V<sub>CC</sub>, V<sub>SD</sub>, and V<sub>TM</sub> do not need to be applied for I<sup>2</sup>C communication. Changes in V<sub>SD</sub> and V<sub>TM</sub> can assert an interrupt when enabled to indicate different power-saving modes (see the *Power-Supply Modes* section).

#### **Busy Interrupt**

When enabled, changes in the BSY bit can assert an interrupt (see the *Busy Indication (BSY)* section).

#### SD Status Interrupt

When enabled, the SDSTAT bit asserts an interrupt for card detection and removal upon entering Card Reader mode for the SD card socket configured as the card reader. The SDSTAT bit is not active during Pass Thru mode and does not change states in the IRQ registers upon card insertion and removal during Pass Thru mode.

Figure 11. I2C\_SEL is connected low to enable simple control and MODE = 1 to enable Card Reader mode for SD card 1.

#### Error Checking

In simple control, the BERR/INT output functions as BERR and indicates if an error occurs during Card Reader mode. If BERR asserts low to indicate an error, the MAX14500–MAX14503 stay in Card Reader mode. If the error clears, data transfer begins. BERR asserts if KVBUS, V<sub>TM</sub>, or V<sub>SD</sub> are not present. It is recommended that MODE be pulled low when BERR indicates an error to return the MAX14500–MAX14503 to Pass Thru mode for the host  $\mu P$  to clear the error.

In I<sup>2</sup>C control, BERR/INT functions as an interrupt output (INT) and asserts for errors encountered in Card Reader mode when interrupts are not masked. To find the source of the interrupt, read the interrupt request registers and status register.

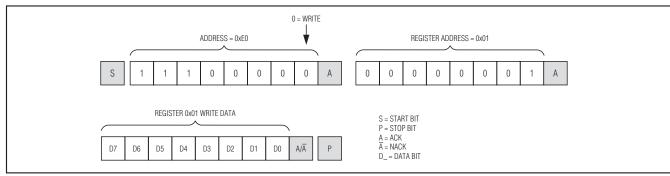

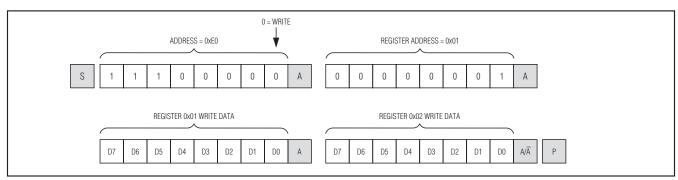

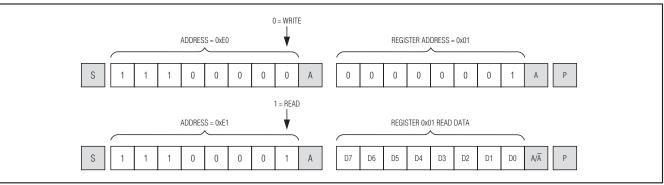

#### **Busy Indication (BSY)**